# Grid Stability Enhancement by a High Voltage SiC MOSFET-Based Asynchronous Microgrid Power Conditioning System

Dingrui Li<sup>1</sup>, Le Kong<sup>1</sup>, Cheng Nie<sup>1</sup>, Xingxuan Huang<sup>1</sup>, Shiqi Ji<sup>1</sup>, Min Lin<sup>1</sup>, Fred Wang<sup>1,2</sup>, and Leon M. Tolbert<sup>1</sup>

<sup>1</sup>Min H. Kao Department of Electrical Engineering & Computer Science, The University of Tennessee, Knoxville, TN, USA <sup>2</sup>Oak Ridge National Laboratory, Oak Ridge, TN, USA

dli35@vols.utk.edu

Abstract—Asynchronous microgrid (ASMG) is a microgrid concept where the ac microgrid is connected to a utility grid through a power conditioning system (PCS). The development of high voltage (HV, >3.3 kV) silicon carbide (SiC) MOSFET technology promotes the implementation of ASMG PCS converters. However, the system-level benefits from SiC MOSFETs have not been well studied for this application. This paper discusses ASMG system stability enhancement resulting from HV SiC MOSFET-based PCS converters. HV SiC MOSFETbased PCS converters can achieve high control frequency, which can benefit the potential harmonic instability caused by the digital control delay. A detailed theoretical analysis is provided, and experimental results for the stability enhancement capability are demonstrated on a converter-based hardware testbed (HTB).

#### Keywords—Asynchronous microgrid, power conditioning system, medium voltage converter, high voltage SiC MOSFET, harmonic stability enhancement.

#### I. INTRODUCTION

Asynchronous microgrids with PCS converters are one of the key application scenarios for future medium voltage (MV) converters [1-2]. In an ASMG, a back-to-back connected ac/dc, dc/ac PCS converter works as the interface of the microgrid to the utility grid. Previous study of ASMG focuses on the system operation benefits resulting from the ASMG structure, including isolation of faults [3], better mode transition performance [4], etc. The recent development of HV SiC devices are starting to facilitate the ASMG PCS implementation. Reference [5] proposed a 10 kV SiC MOSFET-based 3-level neutral point clamped (3L-NPC) converter-based PCS converter. References [6-7] designed and implemented a 10 kV SiC MOSFET-based modular multi-level converter (MMC) for the ASMG PCS.

However, existing research of PCS converters has mainly focused on the converter design [6] and converter-level benefits (size, efficiency, etc.) provided by HV SiC MOSFETs. Systemlevel grid benefits that are driven by the HV SiC MOSFETs still need to be evaluated. Compared with silicon (Si) devices, HV SiC MOSFETs have several advantages such as lower switching loss and faster switching speed [8], which result in higher control frequency and bandwidth. Higher control frequency and bandwidth can lead to shorter digital control delay [9] and better transient performance, which may benefit the ASMG operation.

This paper demonstrates one of the benefits, the grid stabilizer capability provided by the HV SiC MOSFET-based PCS converter. The microgrid is usually supported by multiple distributed energy resources (DERs) with inverter interfaces, which may lead to interaction instability [10]. In the ASMG case, since the main grid and microgrid are decoupled by the PCS, the interactions and disturbances caused by the microgrid are isolated by the PCS. The interaction stability is then determined by the grid side PCS and grid conditions. The digital control delay in the grid side PCS will introduce negative conductance to the PCS output admittance, which reduces the system damping capability and causes instability over a certain frequency range called the non-passive region [11].

The SiC-based PCS may mitigate the instability caused by the control delay as higher control frequency and shorter control delay can be realized. In this paper, the theoretical analysis results show that SiC-based PCS can move the non-passive region to higher frequencies to reduce its impacts on lower-order grid harmonics which are usually difficult to deal with [12]. Moreover, besides PCS control loop stability requirements, the grid interaction stability issue will further limit the control bandwidth of the PCS. By using the SiC-based PCS, higher control bandwidth can be realized considering interaction stability. The experimental verifications are demonstrated on the converter based HTB [13].

The rest of the paper is organized as follows: Section II introduces the ASMG system structure and PCS decoupling capability. Section III provides the output admittance model of grid side PCS. Section IV provides a theoretical analysis of grid stability enhancement capability from HV SiC MOSFET based PCS. HTB test results are demonstrated in Section V, and conclusions are drawn in Section VI.

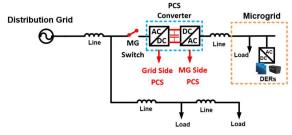

Fig. 1. Asynchronous microgrid (ASMG) concept using two back-toback connected converters,

#### II. ASMG STRUCTURE AND PCS DECOUPLING

## A. ASMG Structure

In an ASMG, the main distribution grid and the microgrid are connected through the PCS converter. As shown in Fig. 1, a PCS converter contains two parts: grid side PCS and microgrid side PCS. There are two operation modes for an ASMG: (1) grid-connected mode and (2) islanded mode. The PCS converter operation in these two modes are different [2].

In the grid-connected mode, the ASMG is part of the main grid. The grid side PCS works as the rectifier to regulate the dclink voltage and provide the main grid with reactive power support; the microgrid side PCS is controlled as a voltage source to regulate the voltage and frequency of the microgrid. The main grid and microgrid share the active power while the reactive power is decoupled by the PCS, meaning that the reactive power of the microgrid is provided locally.

In the islanded mode, the microgrid is disconnected from the main grid and the microgrid side PCS works as a rectifier to regulate the dc-link voltage. In this case, the microgrid voltage and frequency are provided by DERs within the microgrid.

#### B. PCS Decoupling

In an ASMG, since the PCS works as the interface of the microgrid, the grid and microgrid are decoupled by the PCS from multiple perspectives, including frequency decoupling, reactive power decoupling, and impedance decoupling. The frequency decoupling can result in potential asynchronous operation of grid and microgrid, which offers more flexibility for the microgrid frequency regulation. The reactive power decoupling can increase the dispatchable power of the local sources in the microgrid as the reactive power required by the grid is provided by the grid side PCS. The impedance decoupling can potentially benefit the grid stability.

In an interconnected system, the interactions among different subsystems may lead to stability issues. The interaction stability issue can be studied by analyzing the impedance/admittance interactions among subsystems as the impedance/admittance is a representative indicator of the system stability [11].

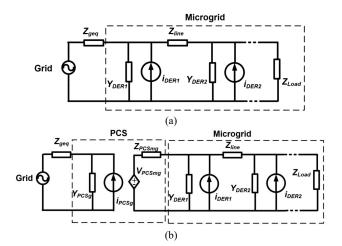

The impedance-based model for the synchronous microgrid (SMG) and ASMG are shown in Fig. 2. In the SMG shown in

Fig. 2. Impedance-based model: (a) SMG case; (b) ASMG case.

Fig. 2(a), the microgrid is directly connected to the main grid, where the DERs and loads in the microgrid will directly interact with the main grid. The DERs are usually connected to the grid with power electronics-based interfaces, and loads' conditions can also vary from time to time. Therefore, the impedance or admittance characteristics of the microgrid are complicated, and the interaction stability is difficult to be guaranteed at all times.

However, for the ASMG shown in Fig. 2(b), the grid and microgrid are decoupled. From the grid side, the equivalent microgrid side admittance is the admittance of the grid side PCS. The stability impacts of the microgrid are mostly determined by the grid side PCS. Although the dc voltage perturbation may also impact the grid side PCS impedance, the impacts are limited and at a relatively low frequency range [14]. Therefore, in this paper, the dc voltage perturbation impacts will not be considered.

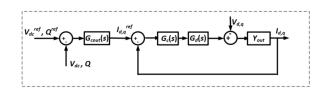

#### III. PCS ADMITTANCE MODELLING AND STABILITY ANALYSIS

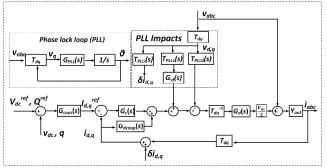

As shown in Fig. 2(b), the output admittance of the grid side PCS can be used to study the microgrid interaction stability with the main grid. In the grid-connected mode, the grid side PCS serves as a rectifier to regulate the dc-link voltage of the PCS and provides the grid with reactive power. The control diagram is shown in Fig. 3, where the dc voltage and reactive power are controlled in dq coordinates. The phase lock loop (PLL) is also realized in dq coordinates to synchronize the PCS with the main grid. Therefore, the admittance of grid side PCS is modelled in dq coordinates, which is an admittance matrix due to the coupling of d and q axis [15]. In this paper, the dc voltage and reactive power loop impacts on the output admittance are not considered as these loops are very slow.

#### A. PCS Admittance Model

The ac output admittance of the grid side PCS is determined by the inverter output passive filter as well as the control loop. As part of the control loop, the PLL will have impacts on the

Fig. 3. Control diagram for grid side PCS.

PCS output admittance characteristics. The PLL introduces a disturbance to the sensed voltage and current during dq transformation and impacts the duty cycle generation during inverse dq transformation. The PLL impact matrices are defined as  $T_{PLLv}$ ,  $T_{PLLd}$ ,  $T_{PLLd}$  in (1)-(3):

$$\boldsymbol{T}_{PLLi} = \begin{bmatrix} 0 & T_{PLL} \boldsymbol{I}_q^c \\ 0 & -T_{PLL} \boldsymbol{I}_d^c \end{bmatrix}$$

(1)

$$\boldsymbol{T}_{\boldsymbol{P}\boldsymbol{L}\boldsymbol{L}\boldsymbol{v}} = \begin{bmatrix} 1 & T_{\boldsymbol{P}\boldsymbol{L}\boldsymbol{L}}\boldsymbol{V}_{\boldsymbol{q}}^{c} \\ 0 & 1 - T_{\boldsymbol{P}\boldsymbol{L}\boldsymbol{L}}\boldsymbol{V}_{\boldsymbol{d}}^{c} \end{bmatrix}$$

(2)

$$\boldsymbol{T}_{PLLd} = \begin{bmatrix} 0 & -T_{PLL}D_q^c \\ 0 & T_{PLL}V_d^c \end{bmatrix}$$

(3)

where  $T_{PLL} = \frac{G_{PLL}}{s+V_d^c G_{PLL}}$  and  $G_{PLL}$  is the proportional-integral (*PI*) controller in the PLL. Subscript *c* represents *dq* value in the controller. The  $G_{vf}$  in the PLL impact loop is a first order filter matrix for the voltage feedforward control, and  $T_{dq}$  is the *dq* transformation matrix. The detailed derivations of the PLL impacts are in [15-16].

Besides PLL, main control loops and passive filter impedance also contribute to the PCS output admittance. In dq coordinates, the admittance matrix  $Y_{out}$  of the PCS inductor filter is in (4):

$$Y_{out} = \begin{bmatrix} sL + R & -\omega L \\ \omega L & sL + R \end{bmatrix}^{-1}$$

(4)

where L and R are filter inductance and resistance. The decoupling term for dq axis is represented by  $G_{dcoup}$  in (5); the *PI* controller matrix is  $G_c$  in (6).

$$\boldsymbol{G}_{decoup} = \begin{bmatrix} 0 & -\omega L \\ \omega L & 0 \end{bmatrix}$$

(5)

$$\boldsymbol{G}_{\boldsymbol{c}} = \begin{bmatrix} k_p + \frac{K_i}{s} & 0\\ 0 & k_p + \frac{K_i}{s} \end{bmatrix}$$

(6)

Moreover, the PCS output admittance should consider the impacts from digital control delay  $G_d$  in (7):

$$\boldsymbol{G}_{\boldsymbol{d}} = \begin{bmatrix} e^{-kT_{c}s} & 0\\ 0 & e^{-kT_{c}s} \end{bmatrix}$$

(7)

where  $T_c$  is the control time, k is the delay cycle, which is usually assumed to be 1.5 in grid-connected inverter cases [16]. Based on (1)-(7), the output admittance is given in (8):

$$Y_{PCSg} = Y_{main} \left( I - G_d T_{dq}^{-1} Y_{PLL} T_{dq}^{-1} \right) \tag{8}$$

where  $Y_{PCSg}$  is the ac output impedance of PCS in dq coordinates;  $Y_{main}$  in (9) is the output impedance contributed by the main control loop, and  $Y_{PLL}$  in (10) is the PLL impact on the output impedance.

$$Y_{main} = \left(1 + Y_{out}G_d T_{dq}^{-1} [G_c - G_{decoup}] T_{dq}\right)^{-1} Y_{out} \quad (9)$$

$$Y_{PLL} = G_{vf}T_{PLLv} - (G_c - G_{deoup})T_{PLLi} - T_{PLLd}$$

(10)

## B. PCS Stablity Analysis

The PCS stability contains two perspectives: the stability of the PCS control loop and the interaction stability between PCS and grid. The stability of the first perspective can be guaranteed by designing PCS controller with a stable closed-loop gain [17].

The stability of the second perspective should consider both the PCS as well as the grid condition. However, actual grid condition can be complicated and changing with time, and the admittance of the grid side PCS may cause instability at different frequency areas. One conservative stability analysis approach is the passivity-based approach, meaning that when the phase of the inverter is within the passive region  $([-90^{\circ}, 90^{\circ}])$ , the inverter will not cause interactive instability when connecting to a passive grid [11].

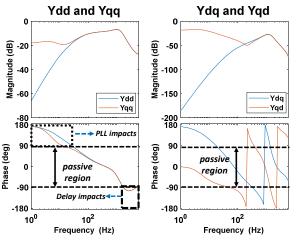

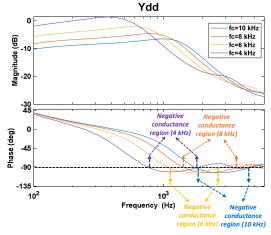

The PCS admittance is studied on a scaled system shown in Table I. The bode plot of grid side PCS admittance is shown in Fig. 4, where all four terms of the admittances contain non-passive frequency region. In the non-passive region, the admittance acts as a negative conductor which reduces the damping capability of the system and can potentially lead to unstable conditions. For the coupling admittances  $Y_{dq}$  and  $Y_{qd}$ ,

| TABLE I. ELECTRICAL PARAMETE | RS |

|------------------------------|----|

|------------------------------|----|

| Parameters                                   | Values                                               |

|----------------------------------------------|------------------------------------------------------|

| DC-link voltage ( $V_{dc}$ )                 | 200 V                                                |

| AC phase voltage $(V_{ac})$                  | 81 V                                                 |

| Current base $(I_b)$                         | 15 A                                                 |

| Fundamental frequency (f)                    | 60 Hz                                                |

| Converter filter impedance                   | <i>L</i> =0.575 mH, <i>R</i> =0.25 Ω                 |

| DC-link capacitor ( $C_{dc}$ )               | 5400 uF                                              |

| Control frequency $(f_c)$                    | 10 kHz                                               |

| Digital control delay $(T_d)$                | 150 us (10 kHz)                                      |

| PI controller parameter (10 kHz)             | $k_p$ =0.027, $k_i$ =12 ( $f_b$ =750 Hz)             |

| PLL parameter                                | $k_{pPLL}$ =0.66, $k_i$ =11.1                        |

| Voltage feedforward filter ( $\omega_{vf}$ ) | $\omega_{vf} = 2 \times \pi \times 10 \text{ rad/s}$ |

| Grid side shunt capacitor $(C_g)$            | 150 uF                                               |

| Grid line impedance                          | $L_g$ =0.575 mH, $R_g$ =0.25 $\Omega$                |

Fig. 4. Grid side PCS output admittance bode plot.

the magnitude of the negative sequence conductance is much smaller than the negative conductance in the main axis admittances  $Y_{dd}$  and  $Y_{qq}$ , meaning that the main axis admittances will have larger impacts on the stability. In this paper, the stability analysis will focus on the main axis admittances.

From Fig. 4, the negative conductance of main axis admittances contains two regions, which are impacted by the PLL [16] and control delay, respectively. The PLL impacts can be reduced by changing the PLL bandwidth or utilizing advanced PLL strategies. The delay impacts can be reduced by delay compensation which may complicate the control design or designing the control system with small delay which may also be difficult as the MV converter usually requires complex control system.

## IV. STABILITY ENHANCEMENT SOLUTION FROM HV SIC MOSFET-BASED PCS

Due to the fast-switching speed and low switching loss of SiC MOSFETs, compared with Si-based PCS, HV SiC MOSFET-based PCS converters can achieve higher control frequency to move the non-passive region, and leave more flexibility for the controller bandwidth design, which can potentially benefit the system stability.

## A. Benefit from Non-Passive Region Moving

From (7), the control delay on each axis is shown in (11)

$$G_{dd,q}(j\omega) = e^{-kT_c s}|_{s=j\omega} = \cos(\omega kT_c) - j\sin(\omega kT_c) \quad (11)$$

where the negative resistance is in the non-passive region  $\left[\frac{f_c}{4k}, \frac{3f_c}{4k}\right]$  and  $f_c$  is the control frequency. Therefore, by increasing the control frequency, the SiC MOSFET-based grid side PCS can move the effective region of control delay to a higher frequency, which may impact the non-passive region of output PCS admittance. Fig. 5 shows the  $Y_{dd}$  for 10 kHz, 8 kHz, 6 kHz, and 4 kHz control frequency, respectively. The PI controller parameters (10 kHz parameters are given as an example in

Fig. 5. *d* axis admittance  $(Y_{dd})$  at different control frequencies (k=1.5).

Table I) are reduced in proportion to the frequency decrease to ensure the stability of the PCS control loop at different frequencies. According to Fig. 5, the negative conductance range of d axis admittance is moving with the control frequency, meaning that the higher control frequency can move the non-passive region of PCS output admittance to a higher frequency.

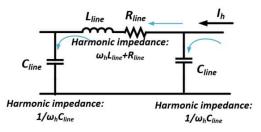

The negative conductance can destabilize the system. In an ASMG, if the grid harmonics are located in the non-passive region or grid impedance interacts with the PCS admittance in the non-passive region, the negative conductance will decrease the damping of grid and can cause potential oscillation in the non-passive region. Fortunately, the line impedance in the grid can dampen high-frequency harmonics. In Fig 6, the  $\pi$  model of the grid lines is utilized to explain the line damping capability [18]. When the frequency of harmonic current increases, the impedance of  $L_{line}$  increases and the impedance of  $C_{line}$  decreases to provide a smaller impedance path, and both changes improve the filtering capability of the harmonic current.

Therefore, when the negative conductance region is increased by the control frequency, the potential oscillation frequency caused by the negative conductance will also increase. When the oscillation frequency is higher, the line damping capability is stronger, and the oscillation impacts are smaller, showing that high control frequency can enhance the grid stability by moving the non-passive region of the PCS admittance to high frequencies.

Fig. 6.  $\pi$  model of the main grid line.

Fig. 7. Simplified control loop for control bandwidth impact analysis.

# B. Benefit to Control Bandwidth from System Stability Perspective

Based on the admittance derivation in (9), the controller matrix  $G_c$  is in the main part of the admittance that can potentially impact the non-passive region of the admittance. The design of the controller parameters can determine the control bandwidth of the PCS. A PCS with higher control bandwidth can respond faster to the grid transients, which will benefit the ASMG dynamic performance.

Next, an examination of the impact of  $G_c$  on the PCS output admittance is conducted. The control diagram in Fig. 3 is simplified to that shown in Fig. 7, where all the disturbances are ignored and only the main control loop is kept. The simplified output admittance can be derived in (12):

$$Y_{PCSgsp} = \frac{1}{\frac{1}{Y_{out}} + G_c G_d},$$

(12)

where all the terms in (12) are scalars and  $Y_{out}$  is shown in (13).

$$Y_{out} = \frac{1}{sL+R} \tag{13}$$

Therefore, combining (11)-(13), the simplified output admittance can be derived in (14)

$$Y_{PCSgsp} = \frac{1}{sL + R + \left(k_p + \frac{k_i}{s}\right)(e^{-kT_cs})}$$

(14)

Then in the frequency domain, it can be written as:

$$Y_{PCSgsp}(j\omega) = \frac{1}{A+jB}$$

(15)

where

$$A = k_p \cos(\omega k T_c) - \frac{k_i}{\omega} \sin(\omega k T_c) + R$$

(16)

$$B = \omega L - k_p \sin(\omega k T_c) - \frac{k_i}{\omega} \cos(\omega k T_c)$$

(17)

Based on (15)-(17), in the non-passive region the real part of the output admittance is determined by the controller parameters, non-passive region frequency, and filter resistance. From (17), two preliminary conclusions can be drawn based on this derivation:

• The non-passive region may be avoided by reducing the controller parameters to meet (18).

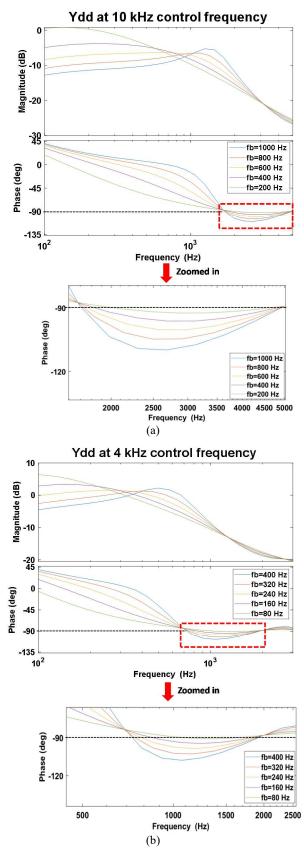

Fig. 8.  $Y_{dd}$  for different control bandwidths: (a) 10 kHz control frequency; (b) 4 kHz control frequency.

The negative conductance value and phase are also impacted by the frequency of non-passive region (when  $\omega$ is larger,  $\frac{k_i}{\omega}$  is smaller,  $\omega L$  is larger).

$$R \ge \max \left| k_p \cos(\omega k T_c) - \frac{k_i}{\omega} \sin(\omega k T_c) \right|$$

(18)

Although these conclusions are drawn based on a simplified control diagram, it can also be known that applying smaller control parameters  $k_p$ ,  $k_i$  and locating the non-passive region at higher frequency can potentially reduce the negative sequence conductance in the non-passive region to benefit the system stability. However, smaller  $k_p$  and  $k_i$  usually mean smaller control bandwidth, meaning that the interaction stability may limit the controller bandwidth.

On the other hand, the frequencies of the non-passive region can also impact the negative sequence conductance value. For the HV SiC MOSFET-based PCS, the non-passive region is moved to higher frequency range, compared with the Si-based PCS, which results in potentially lower negative conductance in the non-passive region, which leaves more margin for the controller bandwidth design.

The bode plot of PCS output admittance in (8) with different control parameters at 4 kHz and 10 kHz are shown in Fig. 8, where the phase margin for the controller is designed at 90° and the control bandwidth decreases. When the control frequency is 10 kHz, the worst phase at 1 kHz control bandwidth is around -110°; When the control frequency is 4 kHz, the worst phase at 400 Hz control bandwidth is around -108°. Also, at 10 kHz, when the control bandwidth is 400 Hz, the worst phase is only -96°. With same control bandwidth, the non-passive region area decreases when the control frequency increases. Therefore, considering the interaction stability, the higher control frequency can leave more margin for the control bandwidth design.

## V. EXPERIMENTAL DEMONSTRATION

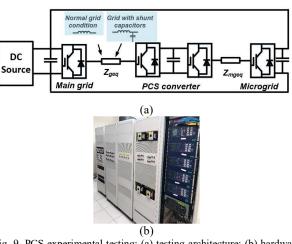

Experimental verifications are realized on a converter-based HTB [13]. The configuration and hardware setup are shown in Fig. 9. The main grid and microgrid are emulated by two-level converters, both for a normal grid condition and for a grid connected with shunt capacitor conditions are emulated. In the testing, the line is emulated with an inductor. The shunt capacitors are applied to emulate a reactive power compensator, which may cause potential oscillations. The parameters are summarized in Table I. Two main cases are applied to demonstrate the non-passive region moving as well as the control bandwidth impacts with considering the interaction stability.

## A. Stability Enhancment by Non-Passive Region Moving

Based on the grid line impedance, inverter impedance and shunt capacitance in Table I, two resonant points are 581 Hz and 784 Hz, meaning that if the non-passive region has

Fig. 9. PCS experimental testing: (a) testing architecture; (b) hardware

intersection with these two frequencies, oscillations may occur. The grid side PCS is tested at 4 kHz and 10 kHz, where the corresponding non-passive regions of 4 kHz operation and 10 kHz operation are [666.7 Hz, 2000 Hz] and [1666.7 Hz, 5000 Hz], respectively. Therefore, the non-passive region of 4 kHz will intersect with the oscillation point, while the 10 kHz operation will not.

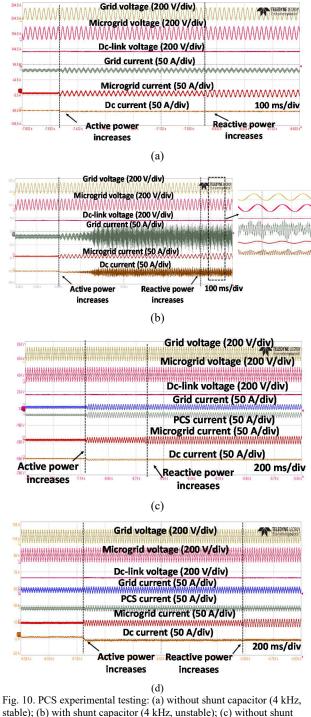

Four cases are tested, and the results are shown in Fig. 10. In Fig. 10 (a) and (b), the grid side PCS is operating at 4 kHz with 300 Hz designed control bandwidth. In Fig. 10(a), no shunt capacitors are applied, and in Fig. 10(b), shunt capacitors are applied. The results show that when the shunt capacitors are applied, the PCS resonates with the main grid while no oscillation occurs when there is no capacitor. The results demonstrate that the PCS control loop is stable, and the oscillation comes from the system interaction.

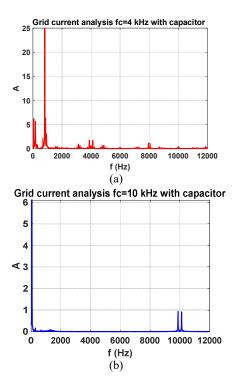

The testing of 10 kHz operation with 750 Hz control bandwidth is shown in Fig. 10(c) and (d), where shunt capacitors are not applied in Fig. 10(c) and applied in Fig. 10(d). The results show that the grid side PCS can work with the main grid without oscillation for both conditions. The FFT analysis for shunt capacitor applied cases of grid current is shown in Fig. 11, where for 4 kHz case, the oscillation occurs at 815 Hz while the 10 kHz case does not have obvious oscillation other than at the switching frequency. Therefore, the testing results can demonstrate that the non-passive region moves with as the control frequency increases, which may avoid oscillation at low frequency.

capacitor (10 kHz, stable); (d) with shunt capacitor (10 kHz, stable).

# B. System Stability Requirements on PCS Control Bandwidth Design

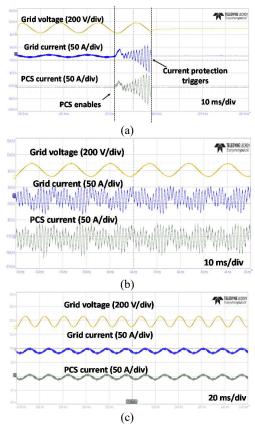

The second testing is realized under 4 kHz by changing the control bandwidth. The control bandwidths for three cases are 400 Hz, 300 Hz, and 200 Hz, respectively. Test results are shown in Fig. 12. When a shunt capacitor is applied, the oscillation is dampened with the control bandwidth decreasing,

Fig. 11. FFT analysis of grid current: (a) with shunt capacitor (4 kHz, unstable); (d) with shunt capacitor (10 kHz, stable).

Fig. 12. Control bandwidth changing at 4 kHz with shunt capacitor: (a) 400 Hz bandwidth; (b) 300 Hz bandwidth; (c) 200 Hz bandwidth.

showing that low control bandwidth can result in better interaction stability. When the control bandwidth is 400 Hz, the oscillation increases and the current keeps increasing. Eventually, the current protection of the emulators is triggered. When the control bandwidth is 300 Hz, the current oscillation also exists but it will not trigger the protection with the same threshold, meaning the damping at this bandwidth is better than 400 Hz. When the control bandwidth is 200 Hz, there is no oscillation observed, showing that the interaction will limit the control bandwidth. In order to increase the control bandwidth, the control frequency needs to be increased.

## VI. CONCLUSION

In this paper, the stability enhancement capability resulting from using a HV SiC MOSFET-based ASMG PCS is analyzed and demonstrated. Based on the analysis of PCS decoupling capability and output admittance derivation, potential interaction stability issues are stated including that the control delay in PCS control loops may cause harmonic instability issues under certain grid conditions. To solve this harmonic issue, either smaller control delay or smaller control bandwidth is required, where SiC devices show advantages compared to similar rated Si devices.

By utilizing HV SiC MOSFET-based PCS with high control frequency, the interaction instability can be eliminated, since it can move the non-passive region in the admittance of PCS to higher frequency to be away from the grid interaction zone. Additionally, high control frequency can provide more flexibility on control bandwidth design considering the interaction stability limitations. By examining several different grid conditions, control frequency and control bandwidth during experimental verifications on a converter-based HTB, the stability enhancement of SiC MOSFET-based PCS is demonstrated.

#### ACKNOWLEDGMENT

This work was supported primarily by the DOE PowerAmerica program at North Carolina State University. The authors thank Southern Company, EPB, and EPC Power for their continuous support of the project. The authors acknowledge Powerex for helping package the 10 kV SiC MOSETs. The authors appreciate Mr. Bob Martin at UTK for supporting the experiments in this paper. This work made use of the Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and DOE under NSF award number EEC-1041877 and the CURENT Industry Partnership Program.

#### REFERENCES

- M. Barnes and P. Binduhewa, "Asynchronous Interconnection of a Microgrid," in *CIRED Seminar*, Frankfurt, Germany, 2008, pp. 64-68.

- [2] D. Li, S. Ji, X. Huang, J. Palmer, F. Wang and L. M. Tolbert, "Controller Development of an Asynchronous Microgrid Power Conditioning System

(PCS) Converter Considering Grid Requirements," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2020, pp. 616-621.

- [3] T. Hong and F. De Leon, "Controlling non-synchronous microgrids for load balancing of radial distribution systems," in *IEEE Transactions on Smart Grid*, vol. 8, pp. 2608-2616, 2016.

- [4] R. Salcedo et al., "Benefits of a Nonsynchronous Microgrid on Dense-Load LV Secondary Networks," in *IEEE Transactions on Power Delivery*, vol. 31, no. 3, pp. 1076-1084, June 2016.

- [5] S. Parashar, A. Kumar, and S. Bhattacharya, "High Power Medium Voltage Converters Enabled by High Voltage SiC Power Devices," in *Proc. International Power Electronics Conference (ECCE Asia)*, 2018, pp. 3993-4000.

- [6] S. Ji, X. Huang, L. Zhang, J. Palmer, W. Giewont, F. Wang, L. M. Tolbert, "Medium Voltage (13.8 kV) Transformer-Less Grid-Connected DC/AC Converter Design and Demonstration Using 10 kV SiC MOSFETs," in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE)*, 2019, pp. 1953-1959.

- [7] D. Li, X. Huang, S. Ji, C. Nie, F. Wang and L. M. Tolbert, "Controller Design and Implementation of a Medium Voltage (13.8 kV) Modular Multi-Level Converter for Asynchronous Microgrids," *IEEE Energy Conversion Congress and Exposition (ECCE)*, 2020, pp. 4642-4648.

- [8] X. Huang, S. Ji, J. Palmer, L. Zhang, L. M. Tolbert and F. Wang, "Parasitic Capacitors' Impact on Switching Performance in a 10 kV SiC MOSFET Based Converter," *IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA)*, 2018, pp. 311-318.

- [9] J. Guo, T. Fan, Q. Li and X. Wen, "Coupling and Digital Control Delays Affected Stability Analysis of Permanent Magnet Synchronous Motor Current Loop Control," *IEEE Vehicle Power and Propulsion Conference* (VPPC), Hanoi, Vietnam, 2019, pp. 1-5.

- [10] W. Cao, Y. Ma, L. Yang, F. Wang and L. M. Tolbert, "D–Q Impedance Based Stability Analysis and Parameter Design of Three-Phase Inverter-Based AC Power Systems," in *IEEE Transactions on Industrial Electronics*, vol. 64, no. 7, pp. 6017-6028, July 2017.

- [11] C. Xie, K. Li, J. Zou and J. M. Guerrero, "Passivity-Based Stabilization of LCL-Type Grid-Connected Inverters via a General Admittance Model," in *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 6636-6648, June 2020.

- [12] Z. Lin, X. Ruan, L. Wu, H. Zhang and W. Li, "Multi resonant Component-Based Grid-Voltage-Weighted Feedforward Scheme for Grid-Connected Inverter to Suppress the Injected Grid Current Harmonics Under Weak Grid," in *IEEE Transactions on Power Electronics*, vol. 35, no. 9, pp. 9784-9793, Sept. 2020.

- [13] Y. Ma, J. Wang, F. Wang, and L. M. Tolbert, "Converter-based reconfigurable real-time electrical system emulation platform," *Chinese Journal of Electrical Engineering*, vol. 4, no. 1, pp. 20-27, 2018.

- [14] I. Vieto and J. Sun, "Refined Small-Signal Sequence Impedance Models of Type-III Wind Turbines," *IEEE Energy Conversion Congress and Exposition (ECCE)*, 2018, pp. 2242-2249.

- [15] W. Cao, X. Zhang, Y. Ma and F. Wang, "Stability criterion and controller parameter design of radial-line renewable systems with multiple inverters," *IEEE Applied Power Electronics Conference and Exposition* (APEC), 2016, pp. 2229-2236.

- [16] B. Wen, D. Boroyevich, R. Burgos, P. Mattavelli and Z. Shen, "Analysis of D-Q Small-Signal Impedance of Grid-Tied Inverters," in *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 675-687, Jan. 2016.

- [17] L. Kong, S. Wang, N. Praisuwanna, F. Wang and L. M. Tolbert, "Stability Analysis and Controller Design of MMC Considering Control Delay," *IEEE Applied Power Electronics Conference and Exposition* (APEC), USA, 2020, pp. 1884-1890.

- [18] S. Zhang, B. Liu, S. Zheng, Y. Ma, F. Wang and L. M. Tolbert, "Threephase short-circuit fault implementation in converter based transmission line emulator," *IEEE Energy Conversion Congress and Exposition* (ECCE), 2017, pp. 2914-292